International Journal of Management, IT & Engineering Vol. 9 Issue 6, June 2019, ISSN: 2249-0558 Impact Factor: 7.119 Journal Homepage: <u>http://www.ijmra.us</u>, Email: editorijmie@gmail.com Double-Blind Peer Reviewed Refereed Open Access International Journal - Included in the International Serial Directories Indexed & Listed at: Ulrich's Periodicals Directory ©, U.S.A., Open J-Gage as well as in Cabell's Directories of Publishing Opportunities, U.S.A

# COMPARATIVE STUDY OF MOSFET, CMOS & FINFETBASE

## RAMAKANT \*

### **Raghvendra Singh**\*\*\*

**Abstract**—In system technology, FinFETs are performed many ways to manipulate leakage cutting-edge, dynamic current, quick channel effects (SCE) and put off over MOSFET and CMOS. FETs are promising substitutes to address quick channel effects (SCEs) higher than the traditional planar MOSFET's at deeply scaled generation nodes and accordingly allow persevered transistor scaling. on this paper, reviewed the comparative take a look at of FinFET with specific parameter related to Channel period, Leakage current, electricity and postpone over MOSFET and CMOS.

<sup>\*</sup> M.Tech. Scholar, EC Department, faculty of Engineering & Technology, and hana Kanpur, Uttar Pradesh, India

<sup>\*\*</sup> Assistant professor in department, electronic & communication engineering, Faculty of Engineering & Technology, Rama University, Kanpur, India

#### **I INTRODUCTION**

During the last three a long time, CMOS era scaling has been a primary driving force of the electronics enterprise and has supplied a course closer to both denser and faster integration. As the dimensions of the transistors is deceased, the thickness of the silicon dioxide gate dielectric has gradually reduced to boom the gate capacitance and thereby drive current, which gives upward push in tool overall performance. The CMOS scaling of the gadgets is facing demanding situations due to shrinking geometries, lower supply voltage, and higher frequencies, this have terrible effect at the device by means of growing quick channel effect due to which leakage (gate leakage and sub-threshold leakage) inside the device is growing constantly [9]. The enhancement in the scaling technology has increased the want of low energy primarily based circuits. In nanometer regime, CMOS based circuit are not be used due to problem in its fundamental cloth, short channel impact and high leakage. The higher technology are wanted for coping with the various effects of MOSFET era [1].because the planar MOSFETs indicates a great SCE (brief Channel impact) and the designers are pay attention to FinFETs, which have negligible SCE for the identical channel period [17]. FinFETs have attracted growing interest during the last decade due to the degrading brief-channel conduct of planar MOSFETs. at the same time as the planar MOSFET channel is horizontal, the FinFET channel (additionally referred to as the fin) is vertical. With a couple of fons and smaller fin heights ends in extra bendy and width of the channel may be increased, which in turn ends in more silicon place. on the other hand, taller fins result in less silicon footprint, but may bring about structural instability. although FinFETs carried out on SOI wafers are very popular. FinFETs have additionally been implemented on conventional bulk wafers appreciably. In [24] authors are finished their paintings on reduction of short channel effects in FinFET. The results screen that leakage cutting-edge due to DIBL is nicely suppressed and roll-off of a FinFET is nicely controlled. Authors in [9] designed a 6T SRAM cell using the FinFET and in comparison SRAM with conventional shape by using varying Sub-threshold leakage cutting-edge and gate leakage modern of inner transistors with self-controllable voltage stage technique. The simulation was carried the use of Cadence Virtuoso tool at 45nm generation and the simulation outcomes indicates that total leakage reduces up to 34% below the self-controllable voltage degree technique.

#### **II. MOSFET devices**

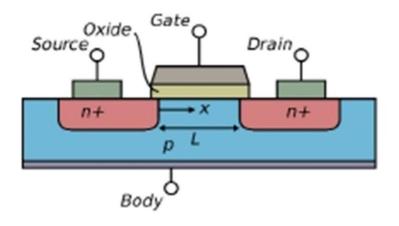

Metal Oxide Semiconductor FET may be very exceptional from that of the Junction FET. both the Depletion and Enhancement type MOSFETs use an electrical field produced with the aid of a gate voltage to alter the go with the flow of price providers, through the semi conductive drainsource channel. In fig 1, suggests that the gate electrode is positioned on the top of a very skinny insulating layer and there are a pair of small regions of n-kinds simply underneath the drain and source electrodes.

#### Fig 1: 2D view of MOSFET

In [26] authors have concluded that lowering the gate dielectric thickness increases the MOSFET drain modern or permits the deliver voltage to be decreased whilst retaining an acceptable drain current and enables the reduction of gate length through the suppression of short-channel outcomes. competitive scaling of CMOS era in latest years has reduced the silicon dioxide (SiO2) gate dielectric thickness. major reasons for difficulty in similarly reduction of the SiO2 thickness include extended poly-silicon (poly-Si) gate depletion, gate dopant penetration into the channel place, and excessive direct-tunneling gate-leakage current, which ends up in questions concerning dielectric integrity, reliability, and stand-with the aid of energy intake. As well identified in improved gate leakage modern in MOSFET is a assignment to continue in the scaling. In [18] authors display that minimize the MOSFETs to the nanometer regime ends in short channel results, which degrades the gadget overall performance and reliability.

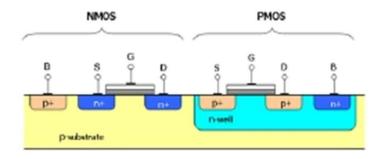

#### III. CMOS

CMOS circuits are built in this type of way that every one PMOS transistors have an enter from the voltage supply or from any other PMOS transistor. similarly, all NMOS transistors have an enter from floor or from another NMOS transistor. Fig 2 suggests the composition of a PMOS transistor, when low voltage is carried out which creates a low resistance between its supply and drain and creates excessive resistance when a high gate voltage is applied. on the other hand, the composition of an NMOS transistor, while a low gate voltage is carried out creates excessive resistance between supply and drain and coffee resistance at a high gate voltage.

Fig 2: 2D view of CMOS

CMOS achieve modern-day reduction by way of emphasize their qualities of every nMOSFET with a pMOSFET and connecting each gates and both drains collectively. A excessive voltage on the gates, with a view to turn on the nMOSFET and pMOSFET will be in off nation, even as a low voltage at the gates will causes the reverse. This association significantly reduces energy intake and heat generation. but, at some point of the switching time of the gate voltage is going from one country to any other country, both MOSFETs behavior in short. This give rise to an abrupt spike in power consumption and arise a extreme issue at excessive frequencies.

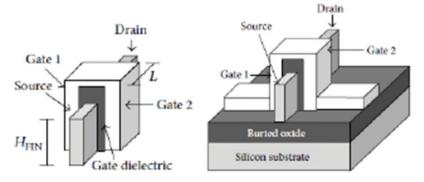

#### **IV. FINFET devices**

Researchers are striving tough to broaden transistor with low price and high overall performance, one such development is a FinFET. It makes use of a fin like structure instead of the conventional flat layout, probable allowing engineers to create faster and more compact circuits and computer chips. The time period "FINFET" describes a non-planar, double gate transistor built on an SOI substrate, primarily based at the unmarried gate transistor design. The crucial characteristics of FINFET is that the engaging in channel is wrapped by using a skinny Si "fin", as shown in fig 3 which paperwork the frame of the device. The fin thickness, which determines the effective channel length of the device [7].

#### Fig 3:3D view of FinFET and SOI FinFET

The FinFET version structure consists of following regions

With very low doping silicon fin area.Poly-silicon region, supply and drain contact location, exceedingly doped. Gate place- oxide (SiO2) tremendous control of brief channel results in submicron regime and making transistors nevertheless scalable. because of this reason, the small-duration transistor may have a bigger intrinsic advantage and much decrease off-kingdom present day in comparison to bulk counterpart. Promising matching behavior. Low value higher technological maturity than planar DG. Suppressed quick Channel impact(SCE) FinFET is one of the promising and higher technologies for its programs and the circuit layout for better overall performance and reliability. In [11] authors are evaluated the performance of FinFET based 6T SRAM mobile in 22nm era. The simulation result indicates that FINFET based totally SRAM design is feasible design in comparison with CMOS based totally SRAM design.effective Channel length (Leffg): maximum of the scaling conduct of FINFET isn't equal to poly period Lg which may be very widespread, but the effective channel length Leffg = Lg-  $\Delta$ L. normally effective length of the transistor may be extracted from measurement or simulation result. but it

isn't a dependable technique. The dependable approach is, by searching the full oxide capacitance Cox as a feature of Lg. The Cox is given by way of

$$Cox = (\varepsilon ox/tox) Weff (Lg-\Delta L)$$

(1)

Gate Capacitance (Cg):- it's miles given with the aid of the relation

$$Cg = Co W L$$

<sup>(2)</sup>

where C0 is the gate capacitance in step with unit region given by using

$$Co = Cr Co / D$$

(3)

wherein, D– Thickness of gate oxide, W – Width of the Channel L – length of the Channel Cr Relative permittivity

Channel Resistance (RC): - it's far given by means of the relation

$$RC = \mu (L / W Qon)$$

(4)

wherein, Qon = Co x Vgs

$\mu$ - Is carrier mobility Vgs – gate to supply voltage

Gate delay (Td): - postpone of the gate may be calculated as

Td = Ron X Cg

(5)

(4.a)

Where in, Cg - Gate capacitance

The values of Gate capacitance, fee in keeping with unit location, Gate capacitance in step with unit region, Gate postpone and hannel resistance may be managed by way of adjusting the Oxide thickness [11].

#### impact on Leakage modern:

In present day CMOS technologies, the sub-threshold leakage current, ISUB, is a good deal large than the opposite leakage modern components. that is specially because of the fairly low threshold voltage in modern-day CMOS gadgets. ISUB is calculated by means of where k and n are capabilities of the generation. And  $\eta$  is the drain-brought about barrier reducing coefficient [21].

#### V. Channel period:s

67

#### VI. Leakage contemporary and Dynamic cutting-edge

revealed that the CMOS devices are shrinking to nanometer regime, growing the effects in brief channel results and versions inside the manner parameters which lead to reason the reliability of the circuit as well as performIn [13], authors have explored the blessings supplied by means of In [11], Authors have ance. The comparative outcomes became proven that FinFET based SRAM design is a possible layout in contrast with CMOS based design at 22nm era. In [21], they found an alternative for low strength interconnect synthesis on the 45nm node using Fin-type fieldeffect Transistors (FinFETs) which are a promising substitute for bulk CMOS at the considered gate lengths. The tested layout approach the output of FinFET SRAM became compared with general CMOS SRAM and the full-size outcomes were acquired that FinFET have more advantage than the CMOS one. In [18], the simulated consequences for FinFET based totally virtual software at nanometer had been acquired that the FinFET device are stepped forward giving higher results than the conventional MOSFET's. In [22], authors are presented the circuit design implication of Ge vs Si PMOS FinFET at the ten nm and seven nm nodes and extracted the internet list from the TCAD. And simulated consequences turned into confirmed that Si always out plays Ge across all critical circuits metrics at 10 nm node and therefore the Si answer remains preferred at 7 nm node. In [7], the fabrication of MOSFET, the minimal channel period were shrinking constantly. As gadgets reduce in addition and similarly, the problems with conventional (planar) MOSFETs are increasing. industry is currently at the 90nm node. As we

cross down to the 65nm, 45nm, 32NM, 22nm, 14nm and many others., nodes, there appear to be no possible alternatives of persevering with forth with the traditional MOSFET. FinFET era gives an opportunity to classical MOSFET to reap low electricity packages and have negligible SCE for the same channel period. In [1], they in comparison the MOSFET with FinFET based totally logic circuit using 32 nm technology, and they found that among all the design FinFET based circuits are more suitable for low strength application in nanometer regime. in this section, Nanometer regime of FinFET are studied and it is discovered in most of the literature that in cutting down the era, FinFETs are appropriate substitute for planar MOSFET's.

multi-gate fin FETs (FinFETs) over traditional bulk MOSFETs. The leakage-postpone saving changed into obtained with returned biasing were explored and evaluated the suitability for low wake-up time and electricity-efficient BB schemes. consequences have been confirmed that 3T and 4T FinFETs are decreased the leakage on the cost of a reasonably worse velocity performance and are well ideal for imposing fast and strength-green adaptive BB techniques. apparently, the better leakage discount performed via 4T FinFETs is because of the higher threshold sensitivity to back biasing became compared to bulk gadgets. In [20], authors are completed an extensive simulation on BOI FinFET and analyzed the effect of underlaps the usage of the TCAD. The simulation of BOI FinFET tool with underlap have been carried out. The incorporation of underlap with BOI FinFET device resulted in a enormous development in SCEs, especially DIBL reduced to 25%, leakage present day decreased to 99% and ION/IOFF extended to 89%. There might be discount in leakage modern-day and electricity dissipation, whilst device is in off condition. The simulations had been discovered that the BOI FinFET structures with underlaps are more efficient than conventional BOI FinFET as undoped underlap place reduces DIBL, leakage cutting-edge(IOFF) and advanced the ION/IOFF ratio. In [21] the leakage present day and dynamic contemporary are analyzed for the FinFET and CMOS primarily based 7T SRAM at 45 nm node. They taken into consideration a mechanism for improving FinFETs efficiency, known as variable-deliver voltage schemes. The transistor stacking at the side of variable deliver voltage operation of FinFETs obtained a larger leakage savings compared to that of bulk gadgets. The simulated outcomes for variant of supply voltage from minimum zero.6V to most of 1V are demonstrated that FinFETS save a larger leakage and dynamic present day. In [12], the leakage cutting-edge brought about by using DIBL was well

suppressed. DIBL takes place while the depletion area of the drain interacts with the source close to the channel floor to lower the source ability barrier. DIBL is improved at better drain voltage and shorter powerful channel duration. floor DIBL is takes place before deep bulk punch-via and it decreased the brink voltage and the leakage cutting-edge. In [2] they designed 6T SRAM cellular the use of the FinFET and as compared it with conventional primarily based 6T SRAM at 45 nm node. The inner transistor sub-threshold leakage modern-day and gate leakage cutting-edge are determined and compared with the conventional structure of 6T SRAM cellular. FinFET SRAM cell is implemented with self-controllable voltage level method and then leakage modern and leakage strength additionally observed. The simulation results had been achieved on Cadence Virtuoso tool at 45nm era had a leakage contemporary in traditional SRAM mobile is 919.3 pA and that of SRAM is 858 pA. The Leakage in SRAM cellular is reduced to ten% the use of FinFET. The resulted general leakage of FinFET SRAM mobile is reduced to 34% once they carried out for self-controllable voltage level technique. We finish that higher reduction in leakage modern and dynamic contemporary is possible in FinFET technology as compared with conventional strategies.

#### VII. strength dissipation

In [21], authors have analyzed for the dynamic electricity for FinFET and CMOS primarily based 7T SRAM at 45 nm node. The simulated results were showed that FinFET saves the more energy than that of CMOS. table I indicates the voltage version scheme for dynamic energy for FinFET at 45 nm node.

#### TABLE I: SIMULATION RESULTS OF FINFET 16 BIT SRAM ARRA

In [11] authors have evaluated and in comparison the performance of CMOS and FinFET primarily based 6T SRAM cell in 22 generation and compared the 6T SRAM for SG/IG mode are performed the dynamic power has 1.38e-04 and leakage power has 1.01e-06 at VDD of 0.8V. among FinFET primarily based

| Parameter         | FinFET |       |       |      |      |

|-------------------|--------|-------|-------|------|------|

| supply<br>voltage | 0.6    | 0.7   | 0.8   | 0.9  | 1    |

| Dynamic           | 34.02  | 313.3 | 630.5 | 1.05 | 1.29 |

| power             | nW     | nW    | nW    | μW   | μW   |

TABLE I: SIMULATION RESULTS OF FINFET 16 BIT SRAM ARRAY

# TABLE II: SIMULATION RESULTS FOR FINFET BASED INVERTER, NAND ANDNOR

| Parameter      |                   |  |

|----------------|-------------------|--|

| supply voltage |                   |  |

|                | Power Dissipation |  |

| Inverter       |                   |  |

| NAND           |                   |  |

| NOR            |                   |  |

SG and IG modes, SG mode design is giving better performance at all of the load stage. In [14], authors have analyzed the process triggered variations on 14-nm technology node silicon on insulator (SOI) FinFET and impact of these variations on postpone and static strength dissipation of FinFET inverter changed into offered. The fin width and peak versions had been taken into consideration that the less effect at the static power dissipation of inverter whereas fluctuation in gate oxide thickness has widespread effect on it. The gate oxide thickness is incremented of 10% which decreased the impact of Lg variability on static energy dissipation to eighty five.28%. The effect of version in static strength turned into minimized by way of deciding on thicker gate oxide as it turned into decreased the gate leakage modern. In [18] they curb the device from 22nm to 14 nm and compared the parameters in each nodes. The power consumption turned into decreased in 14 nm than that of twenty-two nm node. The table II indicates the compared power

dissipation in 22 nm with 14 nm node. In [1], authors have compared the MOSFET and FinFET primarily based good judgment circuits the usage of 32nm generation and discovered that FinFET primarily based circuits are more appropriate for low strength applications in nanometer regime. The strength dissipation is discovered that  $0.247\mu$ W for inverter and zero.131  $\mu$ W and  $0.096 \mu$ W for NAND2 gate, which is low in SG and IG mode. The FinFET based generation has much less energy consumption in comparison with traditional MOSFET and CMOS generation.

#### VIII. delay

In [14] authors have analyzed the FinFET logic circuits in terms of the postpone-tradeoff and in comparison with bulk circuits. They received the postpone saving with returned biasing and evaluated for low wake-up time and energy green BB scheme. In [eleven] they evaluated the performance have been analyzed for FinFET primarily based 6T SRAM and CMOS at 22 nm node. The end result of FinFET based totally 6T SRAM showed that the signal noise margin 000000(SNM) is multiplied to 25.3% in memory cell and it have become 5% faster than CMOS based totally SRAM. In

| Parameter         | CMOS 16 bit SRAM array |             |             |             |             |

|-------------------|------------------------|-------------|-------------|-------------|-------------|

| Supply<br>voltage | 0.6                    | 0.7         | 0.8         | 0.9         | 1           |

| Delay<br>(Write)  | 800.7ps                | 826.1ps     | 826.3<br>ps | 818.5<br>ps | 912.2<br>ps |

| Delay<br>(Read)   | 575.4<br>ps            | 265.2<br>ps | 771.1<br>ps | 776.3<br>ps | 820.3       |

[21]they taken into consideration the operation pace of FinFET SRAM and CMOS array. The examine and write delays are extracted from the characteristic of range of rows. It became observed that the FinFET realized the examine and write operation more or less two times faster

than that of bulk planar one. desk III and IV indicates the in comparison postpone operation for CMOS and FinFET SRAM array

| Parameter           | FinFET 16 bit SRAM array |       |       |       |       |

|---------------------|--------------------------|-------|-------|-------|-------|

| Supply<br>voltage   | 0.6                      | 0.7   | 0.8   | 0.9   | 1     |

| Delay<br>(Write ps) | 200.2                    | 188.3 | 174.5 | 182.1 | 193.7 |

| Delay<br>(Read ps)  | 425.8                    | 254.2 | 229.6 | 224.6 | 229   |

TABLE III: SIMULATION RESULTS FOR CMOS 16 BIT SRAM ARRAY

In [14], authors have simulated the method caused variations on 14 nm technology node silicon on insulator (SOI) FinFET. The effect of process variant at the delay are minimized to 21.13 % and the height of the fin is reduced to 12%. In [18] they lessen the device from 22nm to 14 nm and in comparison the parameters in each nodes. The region covered by way of the tool is reduced. therefore the energy dissipation is also decreased but the delay inside the operation inside the device had been multiplied at 14nm node compared with 22nm. The desk V indicates the as compared effects for 22 nm and 14 nm. FinFET era have high velocity performance.

| Parameter         | 14nm      | 22nm      |

|-------------------|-----------|-----------|

| Supply<br>Voltage | 0.8V      | 0.9V      |

| Inverter          | 74.0142ps | 45.4125ps |

| NAND              | 74.2176ps | 42.4052ps |

| NOR               | 86.2274ps | 51.015ps  |

#### **IX. CONCLUSION**

In this paper, Process technology of FinFET is reviewed and the comparative study of MOS, CMOS and FinFET technologies is carried out. FinFET technology is a good alternative to planar CMOS for scaling beyond 32nm and has superior performance for low power applications.

#### REFERENCES

[1] Aditya waingankar et all.,2016,"Logic Circuits using FinFET: Comparative Analysis" IJSRD, National Conference on Technological Advancement and Automatization in Engineering, January 2016 ISSN:2321-0613.

[2] Anshul Jain et al.,2014, "Optimization of Leakage Current and Leakage Power of FinFET Based 6T SRAM Cell" International Journal of Engineering Technology, Management and Applied Sciences, August 2014, Volume 2 Issue 3, ISSN 2349-4476

[3] Bazizi.E.M et al.,2015, "Advanced TCADSimulation of Local Mismatch in 14nm CMOS Technology FinFET's" SISPAD 2015, September 9-11, 2015, Washington, DC, USA

[4] Bhattacharya D et al., 2014, "FinFETs:from device to architecture- Review Article", Received 4 June 2014; Accepted 23 July 2014; Published 7 September 2014.

[5] Dominique schreurs et al.,2010"Capabilities and Limitations of Equivalent Circuit Models for Modeling Advanced Si FET Devices", MIXDES 2010, 17th International Conference "Mixed Design of Integrated Circuits and Systems", June 24-26, 2010, Wroc\_aw, Poland.

[6] Frank He et al.,2010, "FinFET: From Compact Modeling to Circuit Performance", 2010IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC)

[7] Girish h et all.,2016, "Design of finfet" international journal of engineering research ISSN:2319-6890) (online),2347-5013(print) volume no.5 issue: special 5, pp: 992-1128,20 may 2016

[8] Gracieli Posser et al.,2014, "Performance Improvement with Dedicated Transistor Sizing for MOSFET and FinFET Devices" Conference Paper • July 2014, DOI: 10.1109/ISVLSI.2014.13

[9] Jain A and Saxena M, 2014 "Optimization of Leakage Current and Leakage Power of FinFET Based 6T SRAM Cell" International Journal of Engineering Technology, Management and Applied Sciences, Vol:2, PP 156-163

[10] Khandelwal S et al.,2013 "Leakage current and Dynamic power analysis of FinFET based 7T SRAM at 45nm Technology", International Arab conference on Information Technology (ACIT 2013).